Шина i2c что это

Обновлено: 07.07.2024

I 2 C – двухпроводной интерфейс, разработанный корпорацией Philips. В первоначальном техническом требовании к интерфейсу максимальная скорость передачи данных составляла 100 Кбит/с. Однако со временем появились стандарты на более скоростные режимы работы I 2 C. К одной шине I 2 C могут быть подключены устройства с различными скоростями доступа, так как скорость передачи данных определяется тактовым сигналом.

Протокол передачи данных разработан таким образом, чтобы гарантировать надежный прием передаваемых данных.

Основные термины, используемые при описании работы с шиной I 2 C:

Передатчик – устройство, передающее данные по шине

Приемник – устройство, получающее данные с шины

Синхронизация – процедура синхронизации тактового сигнала от двух или более устройств

Инициализация и завершение передачи данных

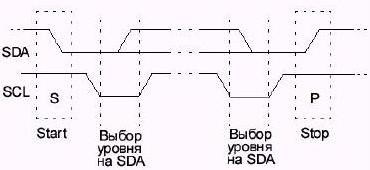

В то время, когда передача данных на шине отсутствует, сигналы SCL и SDA имеют высокий уровень за счет внешнего резистора.

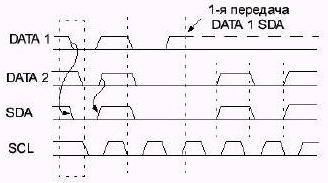

Сигнал START формируется переходом сигнала SDA из высокого уровня в низкий при высоком уровне сигнала SCL. Сигнал STOP определяется как переход SDA из низкого уровня в высокий при высоком уровне SCL. Таким образом, при передаче данных сигнал SDA может изменяться только при низком уровне сигнала SCL.

Адресация устройств на шине I 2 C

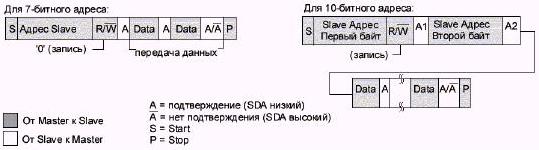

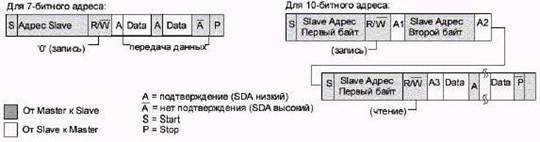

Для адресации устройств используется два формата адреса:

Простой 7-разрядный формат с битом чтения/записи R/W;

и 10-разрядный формат – в первом байте передается два старших бита адреса и бит записи/чтения, во втором байте передается младшая часть адреса.

Подтверждение приема

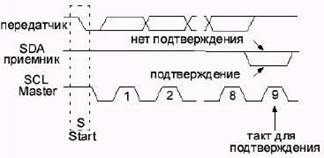

При передаче данных после каждого переданного байта приемник должен подтвердить получение байта сигналом ACK.

Арбитраж

Синхронизация

Синхронизация на шине происходит после выполнения арбитража по отношению к сигналу SCL. При переходе сигнала SCL с высокого уровня в низкий, все заинтересованные устройства начинают отсчитывать длительность низкого уровня. Затем устройства начинают переводить уровень SCL из низкого в высокий согласно требуемой скорости передачи данных. После перехода уровня из низкого в высокое состояние, заинтересованные устройства отсчитывают длительность высокого уровня. Первое устройство, которое переведет сигнал SCL в низкий уровень, определяет параметры тактового сигнала.

none Опубликована: 2005 г. 0 0

Вознаградить Я собрал 0 0

Наконец, подобрались к I2C. Давно хотелось, но всё никак. Тема интересная, а возможности периферии общающейся по этому протоколу могут существенно расширить возможности микроконтроллерной системы. I2C, в отличии от SPI , позволяет наращивать функционал, добавлять новые блоки без изменения в схеме и не задействуя новые выводы МК — настоящий конструктор — стыкуй что и сколько надо =)

Затыков у этой чудо шины два: скорость работы и ограничение на число адресов в сети.

Классически это 100 кбит/с и 128 устройств.

Но стандарт 1992 года предусматривает скорости как 100 кбит/с (low-speed), так и 400 кбит/с (fast-speed) и уже 10-битную адресацию т.е. максимум — 1203 адреса.

А стандартом от 1998, раскрутили аж до 3.4 Мбит/с (Hs-mode).

Но производители живут в прошлом веке и заглянув в датащит на атмеги увидим, что модуль 2-wire Serial Interface может раскочегарится до 400 кГц и адресовать только 127 устройств =\

Так же, есть зарезервированные 8 служебных адресов, так что, на деле, устройств может быть только 120.

Ну и хрен с ними, мне лично — за глаза, да и мороки с этим Hs-mode значительно.

Адреса, обычно, жёстко “прошиты” в микросхему (см. датащиты), но частенько несколько бит адреса “выводят” на ножки — перемычками (на питание или землю) можно задать эти биты и подключить несколько одинаковых микросхем на одну шину.

Есть ещё режим много-мастерной(multi-master) работы — тут сильно выручает соединение “монтажное И”.

А для реализации, непосредственно демократии, на шине действуют ещё и правила джунглей синхронизации и арбитража. Эти правила построены на непрерывном самоконтроле мастерами результатов своей деятельности — отпустит линию — и тут же смотрит — отпустилась? Если — отпустилась, то всё хорошо и он тут пока главный, если нет (кто-то держит линию) — есть мастера потолще, надо свалить.

Естественно, каждый мастер перед началом бурной деятельности по раздаче команд и чтению данных проверяет не занимает ли линию кто-нибудь столь же мастеровитый, и если занимает то тактично ждёт просветов.

А если одновременно, сразу несколько, посмотрели — свободно — воздуха побольше набрали и давай… вещать?

Тут они начинают мериться=)

Во-первых, тактирование. Естественно, все мастера ломанутся дёргать SCL самостоятельно, они ж мастера=) Вот только пока самые резвые (начавшие первыми) сгенерировав первый такт, отпустят линию — более тормозные и неторопливые будут её держать, отпуская по одному, пока не найдётся самый главный тормоз — начавший вещать последним, он то и продолжит, а остальные останутся нервно ждать.

Но, может так случится, что два особо однояйцевых мастера синхронно сгенерят СТАРТ условие. Тогда опять начнётся затяжной заплыв с мериньем. Будут гнать в линию SDA свои нолики и единицы синхронно, пока не обнаружится разница в задуманном — тот кто захочет выставить единицу будет традиционно обломан тем, кто решил в этот момент послать нолик. Обламавшийся перейдёт в ожидание, а тот кто сказал 0 первым — продолжит.

В общем, “0” в I2C решает, на этом всё и держится =)

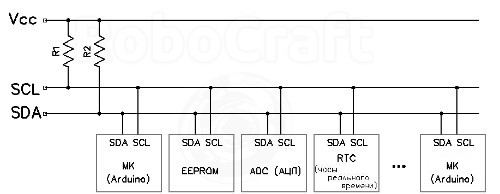

Микроконтроллер на рисунке это ведущий элемент (Master1) им может быть процессор. На рисунке представлено 3 ведомых перефириных элемента Slave В качестве Slave могут быть память, ЦАП, АЦП и пр. К шине может быть подключено до 127 устройств.

Процессор с памятью соединен в данном случае по двум шинам:

SDA (Serial DATA)- шина последовательной передачи данных. Данные по этой шине могут передаваться в двух направлениях.

SCL (Serial Clock) - шина по которой идет тактирование шины данных. Шина синхронизации данных. Она также определяет в какой момент куда пойдут данные. В схеме Master-Master первым битом определяется, кто займет главную роль.

Скорость передачи данных. Так как передаются по 1 биту за 1 такт, то скорость передачи данных составляет 1/8 от тактовой частоты.

Подтверждение при передаче данных обязательно, кроме случаев окончания передачи ведомой стороной. Соответствующий импульс синхронизации генерируется ведущим. Передатчик отпускает (переводит в ВЫСОКОЕ состояние) линию SDA на время синхроимпульса подтверждения. Приёмник должен удерживать линию SDA в течение ВЫСОКОГО состояния синхроимпульса подтверждения в стабильном НИЗКОМ состоянии.

В том случае, когда ведомый-приёмник не может подтвердить свой адрес (например, когда он выполняет в данный момент какие-либо функции реального времени), линия данных должна быть оставлена в ВЫСОКОМ состоянии. После этого ведущий может выдать состояние СТОП для прерывания пересылки данных. Если в пересылке участвует ведущий-приёмник, то он должен сообщить об окончании передачи ведомому-передатчику путём неподтверждения последнего байта. Ведомый-передатчик должен освободить линию данных для того, чтобы позволить ведущему выдать состояние СТОП или повторить состояние СТАРТ.

Синхронизация

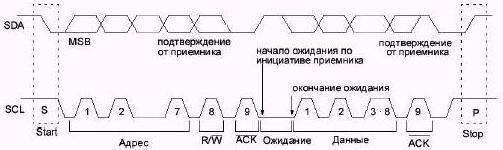

Синхронизация выполняется с использованием подключения к линии SCL по правилу монтажного И. Это означает, что ведущий не имеет монопольного права на управление переходом линии SCL из НИЗКОГО состояния в ВЫСОКОЕ. В том случае, когда ведомому необходимо дополнительное время на обработку принятого бита, он имеет возможность удерживать линию SCL в низком состоянии до момента готовности к приёму следующего бита. Таким образом, линия SCL будет находиться в НИЗКОМ состоянии на протяжении самого длинного НИЗКОГО периода синхросигналов.

Устройства с более коротким НИЗКИМ периодом будут входить в состояние ожидания на время, пока не кончится длинный период. Когда у всех задействованных устройств кончится НИЗКИЙ период синхросигнала, линия SCL перейдет в ВЫСОКОЕ состояние. Все устройства начнут проходить ВЫСОКИЙ период своих синхросигналов. Первое устройство, у которого кончится этот период, снова установит линию SCL в НИЗКОЕ состояние. Таким образом, НИЗКИЙ период синхролинии SCL определяется наидлиннейшим периодом синхронизации из всех задействованных устройств, а ВЫСОКИЙ период определяется самым коротким периодом синхронизации устройств.

Механизм синхронизации может быть использован приёмниками как средство управления пересылкой данных на байтовом и битовом уровнях.

На уровне байта, если устройство может принимать байты данных с большой скоростью, но требует определенное время для сохранения принятого байта или подготовки к приёму следующего, то оно может удерживать линию SCL в НИЗКОМ состоянии после приёма и подтверждения байта, переводя таким образом передатчик в состояние ожидания.

При этом адреса таких однотипных устройств оказываются разнесены в адресном пространстве устройств, подключенных к шине.

В обычном режиме используется 7-битная адресация.

После того, как адрес послан, каждое устройство в системе сравнивает первые семь бит после сигнала СТАРТ со своим адресом. При совпадении устройство полагает себя выбранным как ведомый-приёмник или как ведомый-передатчик, в зависимости от бита направления.

Адрес ведомого может состоять из фиксированной и программируемой части. Часто случается, что в системе будет несколько однотипных устройств (к примеру, ИМС памяти, или драйверов светодиодных индикаторов), поэтому при помощи программируемой части адреса становится возможным подключить к шине максимально возможное количество таких устройств. Количество программируемых бит в адресе зависит от количества свободных выводов микросхемы. Иногда используется один вывод с аналоговой установкой программируемого диапазона адресов[1]. При этом в зависимости от потенциала на этом адресном выводе ИМС, возможно смещение адресного пространства драйвера так, чтобы однотипные ИМС не конфликтовали между собой на общей шине.

Все специализированные ИМС, поддерживающие работу в стандарте шины I²C, имеют набор фиксированных адресов, перечень которых указан производителем в описаниях контроллеров.

Комбинация бит 11110ХХ адреса зарезервирована для 10-битной адресации.

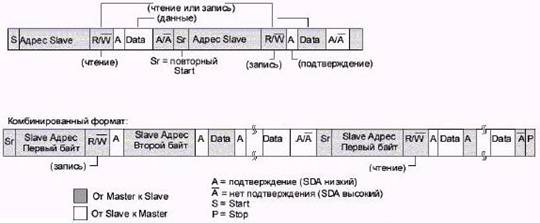

Как следует из спецификации шины, допускаются как простые форматы обмена, так и комбинированные, когда в промежутке от состояния СТАРТ до состояния СТОП ведущий и ведомый могут выступать и как приёмник, и как передатчик данных. Комбинированные форматы могут быть использованы, например, для управления последовательной памятью.

Во время первого байта данных можно передавать адрес в памяти, который записывается во внутренний регистр-защёлку. После повторения сигнала СТАРТа и адреса ведомого выдаются данные из памяти. Все решения об авто-инкременте или декременте адреса, к которому произошёл предыдущий доступ, принимаются конструктором конкретного устройства. Поэтому в любом случае лучший способ избежать неконтролируемой ситуации на шине перед использованием новой (или ранее не используемой) ИМС — следует тщательно изучить её описание (datasheet или reference manual), получив его с сайта производителя. Более того, производители часто размещают рядом более подробные инструкции по применению.

В любом случае по спецификации шины все разрабатываемые устройства должны сбрасывать логику шины при получении сигнала СТАРТ или повторный СТАРТ и подготавливаться к приёму адреса.

Первый стандарт работал на частоте 100 КГц (Standart) Скорость - 100 Кбит/с или 12,5 КБ/с

Затем частота увеличилась до 400 КГц (Fast) Скорость - 400 Кбит/с или 50 КБ/с

Следующий стандарт ввел новые скорости и частоты 1,7 или 3,4 МГц (High) Скорость - (1,7 Мбит/с или 3,4 Мбит/с) 500 КБ/с или 1000 КБ/с

В случаях когда этих скоростей недостаточно используется более быстрый интерфейс SPI

- В покое На шине постоянно положительный потенциал (~3В или 5В но могут быть и другие). А процессор понижая потенциал дает команду на переход к готовности . Для поддержания положительного потенциала возле шины ставяться подтягивающие резистоы (Vdd см. рисунок) на плюсовое питание по обеим линиям. Обчно ставять резисторы на 10 КОм на +3,3 В

1. Связь процессора с памятью (чаще EEPROM)

2. HDMI и DVI интерфейсы (для передачи служебной информации от телевизора к устройству которое воспроизводит видеоконтент, либо для передачи информации от монитора к компьютеру для передачи информации, что за монитор подключили с какими характеристикаи, передача информации от термостата ЦП или информация о скорости вращения кулера и т.д.)

3. Микросхемы и карты памяти (EEPROM, RAM, FERAM, Flash);

4. Доступ к низкоскоростным ЦАП/АЦП;

5. Регулировка контрастности, насыщенности и цветового баланса мониторов;

6. Регулировка звука в динамиках;

7. Управление светодиодами, в том числе в мобильных телефонах;

8. Чтение информации с часов реального времени (кварцевых генераторов);

9. Управление включением/выключением питания системных компонент;

10. Клавиатуры

11. Информационный обмен между микроконтроллерами;

Пример системы с шиной I²C:

На рисунке (Кликабельно):

(a) Высокоинтегрированный телевизор

Микроконтроллер

ФАПЧ-синтезатор

Флеш-память

Мультисистемный декодер сигналов цветности

Стереодекодер звука

Улучшитель сигнала картинки

Hi-Fi аудиопроцессор

Аналоговый видеопроцессор

Декодер телетекста

ИМС сигналов OSD

(b) базовая станция радиотелефона стандарта DECT

Генератор DTMF

Интерфейс телефонной линии

Кодек АДИКМ

Пакетный контроллер

Микроконтроллер

- Первое что надо проверить после БП и тактирования на кварце - Чатсто происходит обрыв подтягивающих резисторов. Диагностируется измерением потенциала на линиях SCL и SDA. Если шина просажена тоесть один из резисторов не додает положительное напряжение, то аппарат может не запускаться.

Шина I2C - назначение, устройство, передача данных, адресация

Создавая электронную схему, многие разработчики сталкиваются с необходимостью применения большого количества промежуточных микросхем для согласования, выборки и адресации отдельных ее блоков. Чтобы свести количество вспомогательных микросхем к минимуму, компания Филипс еще в 80-е годы предложила использовать сетевой последовательный интерфейс с двухпроводной двунаправленной шиной I2C, предназначенную специально для управления несколькими микросхемами в рамках одного устройства.

Сегодня одна только компания Филипс выпускает более сотни I2C-совместимых устройств для электронного оборудования самого разного назначения: памяти, систем видеопроцессоров, аналого-цифровых и цифро-аналоговых преобразователей, драйверов дисплеев и т. д.

Данный протокол позволяет исключить дешифраторы адреса и прочую внешнюю логику согласования. Число микросхем, могущих одновременно работать с шиной I2C, ограничено ее емкостью — максимум 400 пФ.

В I2C-совместимых микросхемах имеется аппаратный алгоритм подавления помех, обеспечивающий сохранность данных даже при сильных помехах. Такие устройства обладают интерфейсом, позволяющим микросхемам связываться между собой даже тогда, когда напряжения их питания различны. На приведенном ниже рисунке можно ознакомиться с принципом соединения нескольких микросхем через одну общую шину.

Каждое из соединенных с шиной устройств имеет свой уникальный адрес, определяется по нему, и, в соответствии с назначением устройства, может работать как приемник либо как передатчик. При передаче данных эти устройства способны быть ведущими (master) или ведомыми (slave). Ведущим выступает то из устройств, которое начинает передачу данных и генерирует синхронизирующие сигналы на линии SCL. Ведомым, по отношению к ведущему, считается при этом устройство-адресат.

В каждый момент действия шины I2C только одно устройство может выступать ведущим, оно формирует на линию SCL сигнал. Ведущий может быть либо ведущим-приемником, либо ведущим-передатчиком.

В принципе шина допускает несколько разных ведущих, накладывая, однако, ограничения на особенности формирования управляющих сигналов и контроля состояния шины; это значит, что несколько ведущих могут начать передачу в один момент, но конфликты такого рода устраняются благодаря арбитражу, то есть способу поведения ведущего при обнаружении факта, что шина занята другим ведущим.

СТАРТ и СТОП

Каждый ведущий создает индивидуальный сигнал синхронизации на линии SCL, когда передает данные по шине.

Подтверждение того, что байт от ведущего-передатчика принят ведомым-приемником, осуществляется выставлением специального подтверждающего бита на линию SDA по завершении приема восьмого бита данных.

ПОДТВЕРЖДЕНИЕ

Итак, отправка 8 бит данных от передатчика - к приемнику завершается формированием дополнительного импульса на линии SCL, когда принимающее устройство выставляет сигнал низкого уровня на линию SDA, показывая что байт целиком им принят.

Подтверждение — неотъемлемая составляющая процесса передачи данных. Ведущий генерирует импульс синхронизации. Передатчик посылает на SDA низкое состояние пока действует подтверждающий синхроимпульс. Пока синхроимпульс пребывает в высоком состоянии, приемник обязан держать SDA в низком состоянии.

Ведущий не имеет права на то, чтобы единолично управлять переходом линии SCL из низкого состояния в высокое. Если ведомому нужно еще время на обработку принятого бита, он может самостоятельно удерживать SCL в низком состоянии до того, пока не будет готов к приему следующего бита данных. Линия SCL в такой ситуации будет пребывать в низком состоянии пока длится самый длинный низкий уровень синхроимпульса.

Устройства с наименее продолжительным низким уровнем будут находиться в состоянии ожидания все то время, пока не завершится длинный период. Когда у всех устройств период низкого уровня синхросигнала закончится, SCL перейдет в состояние высокого уровня.

Все устройства начнут отмечать высокий уровень своих синхросигналов, и первое из устройств, закончивших свой период, первым установит линию SCL в низкое состояние. В итоге продолжительность низкого состояния SCL будет определяться наиболее продолжительным низким состоянием синхроимпульса одного из устройств, а продолжительность высокого — более коротким периодом синхронизации одного из устройств.

Синхронизирующие сигналы могут использоваться приемниками как средство управления передачей данных на битовом и байтовом уровнях.

Если устройство способно на высокой скорости принимать байты, но для этого ему требуется определенное время на процесс сохранения принятого или на подготовку к приему очередного байта, оно может продолжать удерживать SCL в низком состоянии после приема и подтверждения байта, вынужденно удерживая передатчик в состоянии ожидания.

Микроконтроллер без встроенных аппаратных цепей, например, на уровне битов может замедлить частоту синхроимпульсов из-за увеличения длительности их низкого состояния. В результате скорость передачи ведущего будет определяться скоростью медленного устройства.

Каждое подключенное к шине I2C устройство имеет уникальный программный адрес, по которому ведущий обращается к нему, посылая определенную команду. Однотипным микросхемам свойственен селектор адреса, реализуемый либо в виде цифровых входов селектора, либо в аналоговом виде. Адреса разнесены в адресном пространстве подключенных к шине устройств.

По завершении пересылки ведущим байта с адресом, каждый ведомый сравнивает свой адрес с ним. У кого адрес совпадает — тот ведомый и определяет себя как ведомый-передатчик или ведомый-приемник, в зависимости от значения младшего бита байта с адресом.

Адрес ведомого может включать в себя фиксированную и программируемую части. Нередко большое количество однотипных устройств работают в одной системе, тогда программируемая часть адреса позволяет использовать максимум однотипных устройств на шине. То, сколько бит в адресном байте являются программируемыми, зависит от количества свободных выводов микросхемы.

Иногда достаточно одного вывода с аналоговой установкой диапазона программируемых адресов, например SAA1064 – драйвер светодиодного индикатора, имеющий именно такую реализацию. Потенциал на определенном выводе определяет смещение адресного пространства микросхемы так, чтобы микросхемы одного типа не конфликтовали, работая на одной шине. Все микросхемы с поддержкой шины I2C содержат набор адресов, которые производитель указывает в документации.

Последовательный интерфейс I2C (также его обозначается как IIC) довольно популярный последовательный интерфейс. Свою популярность он получил за неплохую скорость передачи информации. В основном до 100 кбит в секунду, а современных устройствах может достигать и до 400 кбит/с, дешевизной и простотой реализации.

Для использования интерфейса понадобиться двухпроводная линия данных и общая линия GND. Линии называются DATA и CLOCK. Линия DATA — по ней передаются/принимаются данные. Линия CLOCK необходима для тактирования. Общее количество абонентов подключаемых к линиям может достигать 128.

Главное устройство называется master ведомое как slave. Генерация тактов осуществляется мастером. Ведомое устройство уведомляет мастера о том что принял байт данных. У каждого абонента должен быть свой уникальный номер. Информация может передаваться только одним абонентом в одну сторону и в определенный временной интервал

Прием и передача данных по I2C

Примем и передача данных происходит когда установки линии в 0, в высокий уровень за счет подтягивающих резисторов она устанавливается сама. Порция передаваемых данных состоит из стартовой посылки, битов и стоповой посылки.

Порядок изменения уровня на шинах задает тип посылки.

После старта передача одного бита данных идет по тактовому импульсу. Другими словами когда линия SCL в низком уровне master или slave устанавливают бит на SDA. Прижимают — в случае 0 или не прижимают — если 1 линию SDA. После этого SCL отпускается и master или slave берут и считывают бит. Получается так что протокол совершенно не зависит от временных интервалов, только от тактовых битов. По этой причине шину I2C очень легко настаивать— для это нужно просто снизить скорость до к примеру 1 байта в минуту и при помощи вольтметра смотреть что происходит.

Если подытожить то передача данных по протоколу I2c происходит следующим образом:

Начало передачи определяет старт последовательность— провал SDA при высоком уровне SCL. При передаче информации от Master к Slave, ведущий генерирует такты на SCL и выдает биты на SDA. Которые ведомый считывает когда SCL становится 1.

При передачи информации от Slave к Master, ведущий генерирует такты на SCL и смотрит что там ведомый творит с линией SDA — считывает данные. А ведомый, когда SCL уходит в 0, выставляет на SDA бит, который мастер считывает когда поднимет SCL обратно.

Заканчивается все STOP последовательностью. Когда при высоком уровне на SCL линия SDA переходит с низкого на высокий уровень.

Другими словами, изменение на шине данных в момент приема данных может быть только когда на линии SCL низкий уровень. Когда SCL в высоком уровне то происходит чтение. В случае если SDA меняется когда SCL в высоком уровне, это означает команды START и STOP.

Когда slave притормаживает, он может сделать так что линия SCL притянется к земле и в результате ведущий не сможет генерировать новые такты. Поэтому мастер должен понять это и дать слейву проработать байт. Поэтому нельзя слепо генерировать такты, при отпускании SCL нужно проверить а поднялась ли она. Если она в низком состоянии то нужно стопануться и подожать пока ведомое устройство ее не отпустит. Далее продолжить с того же места.

Логический уровень

О том как передаются биты стало понятно, теперь нужно разобраться а что же эти биты значат. В интерфейсе I2C добровольно продуманная адресная структура в отличии от интерфейса SPI. Передача данных осуществляется пакетами данных. Пакет состоит из 1 бита отвечающего за подтверждение/не подтверждения приемы и 8 бит данных.

Первый пакет данных идет от master к slave, в котором содержится физический адрес устройства и бит направления.

Устройства подключенный к шине I2C могу работать в двух режимах Master (ведущий) или Slave (ведомый). Передача данных осуществляется сеансами. Ведущий девайс может полностью управлять сеансом:

- начинает сеанс обмена данными;

- контролирует передачу подавая тактовые импульсы на линию Clock;

- завершает сеанс.

Также важно отметить 1 момент, в зависимости от того в каком направлении происходит передача данных и ведущее и ведомее устройство могу быть как приемниками так и передатчиками. К примеру, когда ведущее устройство принимает данные от ведомого то он является приемником, а ведомый выступает в роли передатчика, и наоборот.

Но нужно понимать, что когда Мастер получает данные от slave, мастер не становится slave, он лишь временно принимает данные от slave. Самим процессом передачи данных управляет мастер, он и разрешает слейву передавать данные, путем установки нужного уровня на линии Clock.

Когда данные не передаются, т.е. в режиме ожидания, то линии Data и Clock притянуты к питанию, т. е. находятся в высоком состоянии. Сеанс обмена данными начинается с того что Мастер подает так называемого start-условия, это изменение уровня на линии Data на низкий, при условии что на линии Clock высокий уровень.

После того как было отправлено start-условие, мастер должен сообщить с кем он хочет поговорить и также уточнить что он хочет принять данные либо считать их с устройства.

Каждый бит передаётся за один такт. Та половина такта, во время которой на линии Clock установлен низкий уровень, используется для установки бита данных на шину передающим абонентом (если предыдущий бит передавал другой абонент, то он в это время должен отпустить шину данных). Та половина такта, во время которой на линии Clock установлен высокий уровень, используется принимающим абонентом для считывания установленного значения бита с шины данных.

Читайте также: