Lvds что это в магнитоле

Обновлено: 19.05.2024

Cистема передачи низковольтных дифференциальных сигналов LVDS появилась в 1994 году и была обусловлена потребностями в повышении скорости передачи данных по витой медной паре в компьютерном и коммуникационном оборудовании. Поскольку LVDS является дифференциальной системой, она основана на принципе разности амплитуд напряжения, которые в дальнейшем идентифицируются и сравниваются приемником. Таким образом, передаваемая информация кодируется разностью напряжений на двух проводниках линии связи. Собственная емкость линии связи определяется величиной согласующих резисторов (80…120 Ом), которые подключаются к обоим концам линии связи, а также значением используемой для кодирования информации разности амплитуд напряжений. Например, если драйвер (передатчик) питает линию током 3,5 мА, то на согласующем резисторе будет выделяться мощность примерно 1,2 мВт. Если сравнить это значение с рассеиваемой мощностью 90 мВт, выделяемой на согласующем резисторе линии RS-422, то становится очевидным преимущество LVDS-системы — большая экономичность

LVDS-сигналы в настоящее время широко применяются в высокоскоростных компьютерных шинах. В качестве примеров можно привести FireWire, SCSI, Serial ATA, RapidIO и многие др. Требования к LVDS-системам и сигналам описываются двумя промышленным стандартами. Более распространенным из них является стандарт ANSI/TIA/EIA-644, разработанный ассоциацией телекоммуникационной промышленности США (ассоциация TIA), который описывает общие требования к электрическим характеристикам сигналов. Другой стандарт, разработанный институтом инженеров по электротехнике и электронике (IEEE), описывает специфические требования к LVDS-системе, которая применяется в составе масштабируемого когерентного интерфейса (SCI). Стандарт ANSI/TIA/EIA-644 определяет требования к электрическим характеристикам драйвера и приемника. Требования к протоколу связи не входят в стандарт TIA. Стандарт IEEE 1596.3 SCI-LVDS изначально был ориентирован на дифференциальный PCL-интерфейс, поэтому, SCI-LVDS следует понимать как разновидность интерфейса SCI. Стандарт описывает требования, как к электрическим характеристикам, так и к протоколу кодирования и декодирования передаваемой информации.

Общие сведения о топологиях LVDS-систем

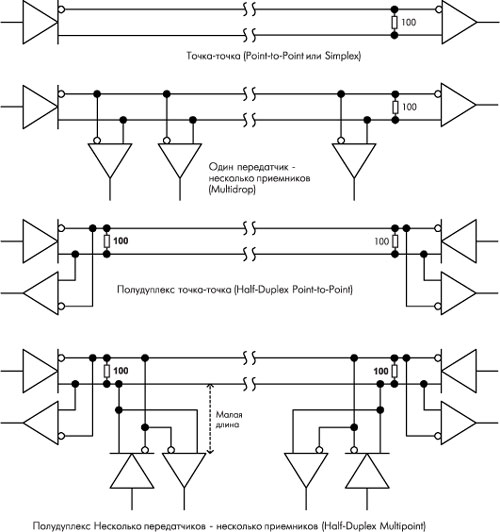

LVDS-система реализуется по одной из трех топологий, представленных на рисунке 1, или их комбинаций. Топология POINT-TO-POINT применяется для построения последовательных или параллельных быстродействующих шин передачи данных. В зависимости от конкретного применения, топология POINT-TO-POINT может быть симплексной (рис. 1а), полудуплексной (рис. 1б) или полнодуплексной (рис. 1в).

Рис. 1. Топологии LVDS-систем

Топология MULTI-DROP используется в системах, в которых несколько LVDS-компонентов необходимо синхронизировать общим LVDS-сигналом синхронизации. Такое решение позволяет добиться максимальной надежности функционирования системы синхронизации. Топология MULTI-DROP также используется в тех случаях, когда одно ведущее устройство передает одну и ту же информацию нескольким подчиненным устройствам, подключенным к общей шине. Топология MULTI-POINT LVDS (или M-LVDS) появилась недавно, ее появление было вызвано потребностями построения систем, в которых несколько LVDS-трансиверов подключаются к общей линии связи. К компонентам такого трансивера (драйвер и приемник) предъявляются несколько иные требования, изложенные в отдельном стандарте TIA/EIA-899. В частности, изменения коснулись пороговых уровней приемника. Стандартом TIA/EIA-899 определяется два типа приемников с различными пороговыми уровнями (см. рис. 2). Кроме того, этим стандартом предписываются особые требования по управлению фронтами сигналов.

Рис. 2. Пороговые уровни LVDS-приемников

Компоненты National Semiconductor для MULTI-DROP-применений

Ранее уже упоминалось, что основным применением топологии MULTI-DROP является построение системы распределенной синхронизации, которая бы обеспечивала высокое быстродействие и малые дрожания. Компания National Semiconductor предлагает широкий выбор продукции для реализации топологии MULTI-DROP, в т.ч. драйверы и приемники с одним (1:1) или несколькими выходами (1:n). Сориентироваться в выборе этой продукции помогут таблица 1 и рисунок 3.

Таблица 1. Краткая характеристика компонентов National Semiconductor для MULTI-DROP-применений

| Наименование | Кол-во драй- веров | Кол-во прием- ников | Совмести- мость входа | Выход | Макси- мальное быстро- действие канала, МГц | Корпус | Примечания |

|---|---|---|---|---|---|---|---|

| Драйверы | |||||||

| DS91C176TM/ D176TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-8 | Полудуплекс, управляемая скорость фронтов |

| DS91C180TM/ D180TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-8 | Полный дуплекс, управляемая скорость фронтов |

| DS92LV010ATM | 1 | 1 | LVDS/ LVPECL/ CML | B-LVDS | 80 | SOIC-8 | Работа при 3,3 или 5 В |

| DS92001TM/ TLD | 1 | 1 | LVDS/ LVPECL/ CML | B-LVDS | 200 | SOIC/ LLP-8 | Управляемая скорость фронтов, флаг LOS |

| DS92LV040ATLQA | 4 | 4 | LVDS/ LVPECL/ CML | B-LVDS | 100 | LLP-44 | Управляемая скорость фронтов, малый перекос |

| Приемники (1:1) | |||||||

| DS91C176TM/ D176TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-8 | Полудуплекс, тип 2/1, широкий диапазон синфазных напряжений |

| DS91C180TM/ D180TM | 1 | 1 | M-LVDS/ LVDS | M-LVDS | 100 | SOIC-14 | Полный дуплекс, тип 2/1, широкий диапазон синфазных напряжений |

| DS90LV012ATMF/ ATLD | 0 | 1 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOT23-5, LLP-8 | Расположение выводов, облегчающее трассировку платы, миниатюрные корпуса |

| DS90LT012ATMF/ ATLD | 0 | 1 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOT23-5, LLP-8 | Расположение выводов, облегчающее трассировку платы, миниатюрные корпуса |

| DS90LV028ATM | 0 | 2 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOIC-8 | Расположение выводов, облегчающее трассировку платы |

| DS90LV048ATM/ ATMTC | 0 | 4 | LVDS/ LVPECL/ CML | LVTTL | 200 | SOIC/ TSSOP-16 | Расположение выводов, облегчающее трассировку платы |

| Приемники (1:n) | |||||||

| SCAN90CP02SP/ VY | 2 | 2 | LVDS/ LVPECL/ CML | LVDS | 750 | LLP-28/ LQFP-32 | Програм- мируемая коррекция предыска- жений, интерфейс JTAG, 1149.6 |

| DS90CP04TLD | 4 | 4 | LVDS/ LVPECL/ CML | LVDS | 1250 | LLP-32 | Очень малые дрожания, малое посадочное место |

| DS92CK16TMTC | 1 | 6 | LVDS/ LVTTL | VTTL и B-LVDS | 125 | TSSOP-24 | Поддержи- ваемые конфигура- ции: A) LVTTL-вход, до 6 LVTTL- + 1 BLVDS-выходов B) LVDS-вход, до 6 LVTTL-выходов |

| DS90LV110ATMT | 1 | 10 | LVDS/ LVPECL/ CML | LVDS | 200 | TSSOP-28 | Малые дрожания выходных сигналов |

| Прим.: Вся продукция рассчитана на работу в промышленном температурном диапазоне: -40…85°С. | |||||||

Рис. 3. Компоненты National Semiconductor для MULTI-DROP-применений

Рис. 4. Расположение выводов DS91C176/DS91D176 и DS91C180/DS91D180

LMP8100 — усилитель с программируемым коэффициентом усиления

Операционный усилитель LMP8100A дает гарантированную точность усиления 0,03 % в диапазоне от 1 В/В до 16 В/В (с шагом 1 В/В) во всем индустриальном диапазоне температур от -40 до 125°С.

Компания National Semiconductor представила LMP8100, полупрецизионный PGA-усилитель с программной точностью установки коэффициента усиления 0,075% при температурном диапазоне от

-40 до 85°С. Коэффициент усиления устанавливается с помощью массива из 16-ти прецизионных тонкопленочных резисторов. Ядром PGA усилителей является 33 МГц ОУ с CMOS-выходами, rail-to-rail, с типичным коэффициентом усиления 110 Дб.

Отличительные характеристики LMP8100

LMP8100 обеспечивает четыре уровня внутренней частотой компенсаций, которые при высоких значениях коэффициента усиления расширяют значение ширины полосы пропускания сигнала. Их встроенная опция калибровки нуля выхода позволяет пользователю измерить выходной сдвиг напряжения для калибровки уменьшения ошибок от температуры и напряжения.

Режим работы усилителя программируется через последовательный порт, что позволяет управлять несколькими усилителями LMP8100 от одного последовательного порта микроконтроллера. Устройство имеет регистр управления усилителя и двойную буферизацию, что позволяет избежать ошибок между записями установок.

LMP8100 имеет скорость нарастания 12 В/мс и полосу пропускания 33 МГц. Диапазон напряжения питания от 2,7 В до 6,5 В с током потребления 5,3 мА, выходной ток 20 мА. В режиме энергосбережения ток потребления падает до 20 мА.

LMP8100 построены на технологическом процессе VIP50 BiCMOS и способны кардинально улучшить точность системы и уменьшить их энергопотребление.

В последнее время среди всевозможных шинных и интерфейсных решений все чаще выделяют скоростной и достаточно неприхотливый интерфейс LVDS. Его применение позволяет достичь скорости передачи до 400–600 Мбит/c по одной паре, причем практически без применения всевозможных экзотических элементов. В этой статье рассматривается не только сам интерфейс LVDS, но и вопросы его применения, построения LVDS-каналов и интеграцию их в состав устройства. Причем основное внимание уделяется не предельным показателям, достигнутым в лабораторных условиях, а именно рекомендациям по проектированию реальных решений на основе доступных компонентов, которые могут быть применены в реальных устройствах, чтобы помочь разработчикам в решении проблем.

Как вариант транспорта для межмодульного и межкорпусного обмена мы рассмотрим стремительно набирающий популярность интерфейс LVDS. Созданный как достаточно специфический стандарт обмена для подключения LCD-матриц в мобильных компьютерах, интерфейс LVDS показал себя недорогим и удобным решением. В его силах организация сверскоростного обмена между микросхемами на плате, минимизация количества линий за счет перевода из параллельной в последовательную передачу по LVDS, обеспечение скоростного межмодульного соединения на расстояние до нескольких метров по кабелю, организация скоростных шинных решений.

При этом LVDS-каналы не требуют каких-либо специфических и дорогостоящих материалов, а просто огранизуются на обычной печатной плате и работают по недорогим кабелям, таким как, например, широко известный и доступный кабель CAT5.

Рис. 1. Метод передачи интерфейса LVDS

Метод передачи

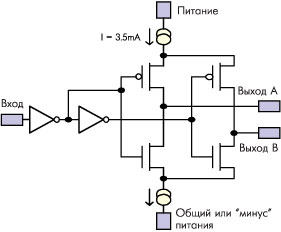

Интерфейс LVDS использует дифференциальную передачу сигналов с малыми сигнальными уровнями. На рис. 1 показана схема передачи одного канала LVDS. Передатчик управляет дифференциальной линией. В линию выдается токовая посылка с током 3,5 мА. Нагрузкой линии служат параллельно включенные дифференциальный LVDS-приемник и 100 Ом резистор. Сам приемник имеет высокое входное сопротивление, и основное формирование сигнала происходит на нагрузочном резисторе. При токе линии 3,5 мА на нем формируется падение напряжения 350 мВ, которое и детектируется приемником. При переключении направления тока в линии меняется полярность напряжения на нагрузочном резисторе, формируя состояния логического нуля и логической единицы.

Используемая схема передачи имеет целый ряд преимуществ.

LVDS-интерфейс имеет высокую скорость передачи данных. Определенная стандартом максимальная скорость составляет до 622 Мбит/с, что сравнимо с оптическим интерфейсом. При этом реальное быстродействие LVDS-канала ограничивается двумя факторами: скоростью подачи и съема данных и параметрами среды передачи.

Используемый дифференциальный метод передачи сигналов позволяет максимально снизить влияние внешних наводок. Малое изменение напряжения, симметричные линии передачи и низкое нарастание напряжения (1 В/нс) обусловливают малый уровень наводок от самого интерфейса. В свою очередь, малый уровень перекрестных наводок и низкая чувствительность к внешним наводкам позволяют использовать высокую плотность соединений как на печатной плате, так и в кабеле. Метод передачи LVDS не зависит от напряжения питания и работает при напряжении питания передатчика и приемника 5 В, 3 В или 2,5 В. При этом сопряжение устройств с разным напряжением питания не является проблемой.

Используемый метод передачи позволяет также существенно снизить энергопотребление интерфейса. На 100 Ом нагрузке LVDS при падении напряжения 400 мВ составляет 1,2 мВт. Для сравнения, интерфейс RS-422 имеет рассеиваемую мощность на нагрузке порядка 90 мВт, что в 75 раз больше.

Следует отметить и простоту терминирования сигнальных LVDS-линий — для этого требуется всего один резистор для каждой пары, и все. Для сравнения, другие скоростные методы требуют пары резисторов, один из которых подключается на землю, а второй к питанию, причем зачастую не напрямую, а через специальный источник.

LVDS-стандарт

LVDS-интерфейс описывается двумя стандартами: ANSI/TIA/EIA-644 и IEEE 1596.3. TIA-644 — общий стандарт. Он описывает электрическую часть интерфейса — выходные и входные параметры приемника. Стандарт не включает в себя функциональное описание, протокол обмена или полные характеристики кабеля, поскольку все это зависит от приложения.

Разрядность и быстродействие контроллеров, процессоров и изделий на их основе постоянно возрастают. Производительность всей системы сильно зависит от скорости обмена данными между устройствами. В последнее время для этого вс╦ чаще используют высокоскоростные интерфейсы LVDS (Low-Voltage Differential Signaling или дифференциальный метод передачи с использованием сигналов низкого уровня) и M-LVDS (Multipoint-LVDS или многоточечный двунаправленный способ обмена информацией). Они позволяют организовать сверхскоростной обмен между микросхемами на печатной плате, а также эффективное взаимодействие между блоками и стойками. На передающей стороне параллельный код преобразуется в последовательный. На принимающей - выполняется обратное преобразование информации. Такой способ обмена позволяет существенно уменьшить количество соединительных проводников, сократить габариты разъемов при увеличении надежности и уменьшении стоимости всего комплекса.

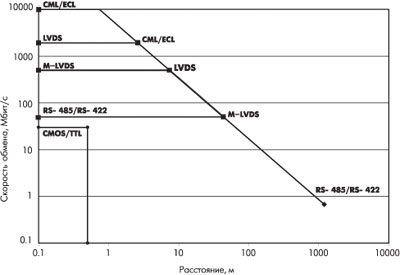

На рис. 1 показаны соотношения скорости обмена и допустимого расстояния для разных интерфейсов. Обратите внимание, что масштаб по осям логарифмический! Из рис. 1 очень хорошо видно, что каждый тип интерфейса имеет свою нишу и предназначен для определенных областей применения. Основное назначение любого последовательного интерфейса - "сворачивание" параллельного кода в скоростной последовательный канал и "разворачивание" последовательного кода в параллельный на приемной стороне.

При расстояниях до 30 м и скоростях передачи менее 50 Мбит/с обычно используют интерфейсы стандартов TIA/EIA-422 (RS-422, multidrop) и TIA/EIA-485 (RS-485, multipoint). Выходные дифференциальные сигналы высокого уров-ня, чувствительные приемники и работоспособность при уровнях помех до 7 В - их положительные качества для обеспечения эффективного обмена данными между удаленным оборудованием. Для скоростей передачи более 50 Мбит/с или в устройствах, где очень важно низкое потребление энергии, применяют интерфейсы LVDS или M-LVDS. Передача и прием со скоростью около 10 Гбит/с обеспечивается эмиттерно-связанной логикой (ECL - emitter-coupled logic) или положительной эмиттерно-связанной логикой (PECL - positive ECL). Однако такая высокая скорость обмена достигается за счет увеличения стоимости при сильном росте потребляемой мощности.

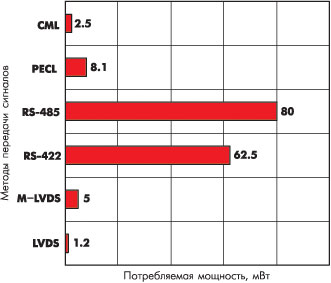

Немаловажным параметром является экономичность каждого типа интерфейса. На рис. 2 показана диаграмма потребления мощности некоторыми интерфейсами и типами логики. Стоит отметить, что LVDS и M-LVDS занимают лидирующие позиции по этому параметру. Вдобавок к этому, только что отмеченные интерфейсы работоспособны при самых низких питающих напряжениях среди показанных на рис. 2.

Благодаря токовому выходу оконечного каскада (рис. 3), потребляемая мощность LVDS и M-LVDS практически не зависит от скорости передачи информации.

Эти положительные особенности особенно важны для автономных и портативных устройств. Сигналы низкого уровня и дифференциальная схема передачи существенно облегчают решение проблемы электромагнитной совместимости, что добавляет очки в копилку положительных качеств рассматриваемых интерфейсов LVDS и M-LVDS.

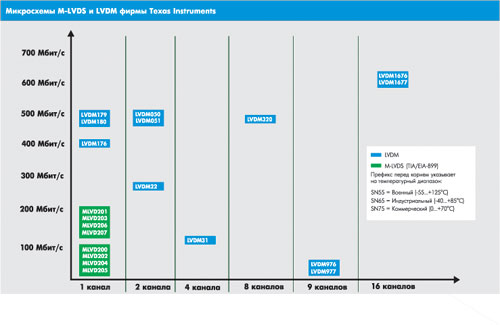

На рис. 4 показан обзор микросхем интерфейсов LVDS фирмы Texas Instruments. Некоторые из них позволяют получить скорость обмена до 2 Мбит/c. Но как для спортивного скоростного автомобиля требуется специальная трасса, так и для достижения сверхвысоких скоростей обмена данными необходим тщательный подход к проектированию всего тракта передачи и приема.

На рис. 5 показаны возможные способы обмена между устройствами. Simplex (точка-точка) позволяет передавать информацию только в одну сторону и только одному приемнику. На приемной стороне тракта передачи обязательно наличие согласующего резистора (терминатора). Вариант Multidrop содержит в своем составе один передатчик и несколько приемников (каждый из них располагается рядом с основной линией передачи). И в этом случае необходимо наличие только одного резистора для устранения отраженных сигналов.

Полудуплекс позволяет организовать двухсторонний обмен данными, но с разделением во времени, то есть в любой момент времени передача информации может происходить только в одном направлении (отсюда и приставка полу-). При полудуплексе точка-точка обмен происходит только между двумя устройствами. При многоточечном полудуплексе (Multipoint) двухсторонний обмен возможен между любыми устройствами, но опять же с условием временного разделения потоков информации. В этом случае терминальные резисторы должны быть установлены на обеих сторонах основного канала передачи и приема (рис. 5).

Интерфейсы LVDS (один передатчик - несколько приемников, стандарт TIA/EIA-644) не позволяют напрямую организовать двунаправленный многоточечный обмен, как это возможно с помощью интерфейсов RS-485 (стандарт TIA/EIA-485). Для создания многоточечного полудуплексного режима "Несколько передатчиков - несколько приемников на одной шине" фирмами Texas Instruments и National Semiconductor был создан многоточечный интерфейс M-LVDS (стандарт TIA/EIA-899-2001), с помощью которого возможен двухсторонний обмен данными (Half-Duplex Multipoint - многоточечный полудуплекс). M-LVDS - это высокоскоростной экономичный многоточечный RS-485, позволяющий создать сеть, включающую в себя до 32 узлов со скоростью обмена до 500 Мбит/c.

На рис. 5 представлены микросхемы M-LVDS и LVDM интерфейсов Texas Instruments.

Интерфейсные микросхемы LVDM имеют в два раза более мощный токовый выход. Это необходимо при работе на линию с двумя согласующими резисторами (полудуплексный обмен). Эти приборы были специально разработаны для создания скоростной шинной архитектуры M-LVDS. У фирмы National Semiconductor подобные микросхемы называются BusLVDS или BLVDS. Для LVDM и BusLVDS выходной ток лежит в пределах от 8 до 10 мА. Для M-LVDS - около 11 мА.

В номенклатуре Texas Instruments есть и LVDT-интерфейсы. Наличие буквы "Т" говорит о том, что внутри микросхемы имеется встроенный согласующий резистор (терминатор) сопротивлением около 100 Ом. Следует учесть, что LVDT-микросхемы можно устанавливать только на оконечных (основных) узлах основного тракта, так как на промежуточных узлах согласующие резисторы не нужны.

В табл. 1 приведены основные типы микросхем для шинной архитектуры M-LVDS.

В табл. 2 показано соответствие между некоторыми микросхемами интерфейсов LVDS и M-LVDS ведущих мировых производителей.

Fairchild - Fairchild Semiconductor; NSC - National Semiconductor; Maxim - Maxim

Integrated Products; Philips - Philips Semiconductors; Pericom - Pericom Semiconductor.

*) F - функционально близкий, но не полный эквивалент; P - близкое соответствие, но не pin-for-pin (отличаются расположением выводов); Q - близкая функциональность и совпадение по выводам, но не полный эквивалент; S - полное совпадение по функциональности и по выводам.

Каналы LVDS и M-LVDS имеют в своей основе недорогие материалы (легко создаются на печатной плате или с помощью широко распространенного кабеля CAT5). Рассмотренные скоростные интерфейсы выпускаются многими известными компаниями, что значительно расширяет выбор при построении скоростной сети различного уровня сложности.

При необходимости Вы можете обратиться в центр информационно-технической поддержки (EPIC) фирмы Texas Instruments.

За дополнительной информацией обращайтесь к сотрудникам фирмы КОМПЭЛ по адресам:

Низковольтной дифференциальной передачи сигналов , или LVDS , также известный как TIA / EIA-644 , представляет собой технический стандарт , который определяет электрические характеристики дифференциала , последовательный стандарт сигнализации, но это не является протоколом. LVDS работает с низким энергопотреблением и может работать на очень высоких скоростях с использованием недорогих медных кабелей с витыми парами . LVDS - это только спецификация физического уровня; многие стандарты и приложения передачи данных используют его и добавляют поверх него уровень канала передачи данных, как определено в модели OSI .

LVDS был представлен в 1994 году и стал популярным в таких продуктах, как ЖК-телевизоры, автомобильные информационно-развлекательные системы, промышленные камеры и машинное зрение, ноутбуки и планшетные компьютеры , а также системы связи. Типичными приложениями являются высокоскоростное видео, графика, передача данных видеокамер и компьютерные шины общего назначения .

Раньше производители ноутбуков и ЖК-дисплеев обычно использовали термин LVDS вместо FPD-Link, когда ссылались на свой протокол, а термин LVDS по ошибке стал синонимом Flat Panel Display Link в инженерном словаре видео-дисплеев.

СОДЕРЖАНИЕ

Дифференциальная и несимметричная сигнализация

LVDS - это система дифференциальной сигнализации , означающая, что она передает информацию как разность напряжений на паре проводов; Напряжения двух проводов сравниваются на приемнике. В типовой реализации передатчик подает в провода постоянный ток 3,5 мА , при этом направление тока определяет цифровой логический уровень. Ток проходит через согласующий резистор приблизительно от 100 до 120 Ом (согласованный с характеристическим сопротивлением кабеля для уменьшения отражений) на приемном конце, а затем возвращается в противоположном направлении по другому проводу. Из закона Ома , разность напряжений на резисторе поэтому около 350 мВ . Приемник определяет полярность этого напряжения для определения логического уровня.

Пока между двумя проводами существует тесная связь по электрическому и магнитному полю, LVDS снижает генерацию электромагнитного шума. Это уменьшение шума происходит из-за равного и противоположного тока, протекающего по двум проводам, создавая равные и противоположные электромагнитные поля, которые имеют тенденцию гасить друг друга. Кроме того, плотно связанные провода передачи уменьшают восприимчивость к электромагнитным шумовым помехам, поскольку шум в равной степени влияет на каждый провод и проявляется как синфазный шум. На приемник LVDS не влияют синфазные помехи, поскольку он воспринимает дифференциальное напряжение, на которое не влияют изменения синфазного напряжения.

Тот факт, что передатчик LVDS потребляет постоянный ток, также предъявляет гораздо меньшие требования к развязке источника питания и, таким образом, создает меньше помех в линиях питания и заземления передающей цепи. Это уменьшает или устраняет такие явления, как дребезг заземления, которые обычно наблюдаются в несимметричных линиях передачи с оконечной нагрузкой, где высокие и низкие логические уровни потребляют разные токи, или в линиях передачи без оконечной нагрузки, где ток появляется внезапно во время переключения.

Низкое дифференциальное напряжение, около 350 мВ, приводит к тому, что LVDS потребляет очень мало энергии по сравнению с другими технологиями передачи сигналов. При напряжении питания 2,5 В мощность для управления 3,5 мА становится 8,75 мВт по сравнению с 90 мВт, рассеиваемыми нагрузочным резистором для сигнала RS-422 .

| V ee | V ПР | V OH | V куб. | V CMO |

|---|---|---|---|---|

| GND | 1,0 В | 1,4 В | 2,5–3,3 В | 1,2 В |

LVDS - не единственная используемая система дифференциальной сигнализации с низким энергопотреблением , другие системы включают последовательный ввод / вывод Fairchild Current Transfer Logic.

Приложения

В 1994 году компания National Semiconductor представила LVDS, который позже стал де-факто стандартом высокоскоростной передачи данных.

LVDS стал популярен в середине 1990-х годов. До этого разрешения компьютерных мониторов были недостаточно большими, чтобы требовать таких высоких скоростей передачи данных для графики и видео. Однако в 1992 году Apple Computer потребовался способ передачи нескольких потоков цифрового видео без перегрузки существующей шины NuBus на объединительной плате . Apple и National Semiconductor ( NSC ) создали QuickRing , первую интегральную схему, использующую LVDS. QuickRing представлял собой высокоскоростную вспомогательную шину для видеоданных для обхода NuBus в компьютерах Macintosh. В мультимедиа и суперкомпьютерных приложений продолжает расширяться , поскольку оба необходимы для перемещения больших объемов данных по каналам длиной в несколько метров (с диска на рабочей станции , например).

Первое коммерчески успешное применение LVDS было в портативных компьютерах, передающих видеоданные с графических процессоров на плоские дисплеи с помощью Flat Panel Display Link от National Semiconductor. Первый набор микросхем FPD-Link уменьшил 21-битный видеоинтерфейс и тактовую частоту до 4 дифференциальных пар (8 проводов), что позволило ему легко пройти через петлю между дисплеем и ноутбуком и воспользоваться преимуществами низкого уровня LVDS. шумовые характеристики и высокая скорость передачи данных. FPD-Link стал де-факто открытым стандартом для этого портативного приложения в конце 1990-х годов и до сих пор остается доминирующим интерфейсом дисплея в портативных и планшетных компьютерах. По этой причине производители микросхем, такие как Texas Instruments, Maxim, Fairchild и Thine, производят свои версии набора микросхем FPD-Link.

Приложения для LVDS расширились до плоских дисплеев для потребительских телевизоров по мере увеличения разрешения экрана и глубины цвета. Для обслуживания этого приложения наборы микросхем FPD-Link продолжали увеличивать скорость передачи данных и количество параллельных каналов LVDS, чтобы удовлетворить внутренним требованиям телевидения для передачи видеоданных от главного видеопроцессора к контроллеру синхронизации панели дисплея. FPD-Link (обычно называемый LVDS) стал де-факто стандартом для этого внутреннего ТВ-соединения и остается доминирующим интерфейсом для этого приложения в 2012 году.

Следующим целевым приложением была передача видеопотоков через внешнее кабельное соединение между настольным компьютером и дисплеем или DVD-плеером и телевизором. NSC представил более производительные дополнения к FPD-Link, названные LVDS Display Interface (LDI) и стандартами OpenLDI . Эти стандарты допускают максимальную частоту пикселей 112 МГц, что достаточно для разрешения дисплея 1400 × 1050 ( SXGA + ) при частоте обновления 60 Гц. Двойное соединение может повысить максимальное разрешение дисплея до 2048 × 1536 ( QXGA ) при 60 Гц. FPD-Link работает с кабелями длиной до 5 м, а LDI - до 10 м. Тем не менее, цифровой визуальный интерфейс (DVI), использующий TMDS по сигналам CML, выиграл соревнование по стандартам и стал стандартом для внешнего подключения настольных компьютеров к мониторам, а HDMI в конечном итоге стал стандартом для подключения цифровых видеоисточников, таких как DVD-плееры, к плоским дисплеям на бытовой Приложения.

Еще одно успешное приложение LVDS - Camera Link - это протокол последовательной связи, разработанный для приложений компьютерного зрения и основанный на наборе микросхем NSC под названием Channel Link, который использует LVDS. Camera Link стандартизирует видеоинтерфейсы для научных и промышленных продуктов, включая камеры, кабели и устройства захвата кадров. Ассоциация автоматизированной визуализации (AIA) поддерживает и администрирует стандарт, потому что это глобальная отраслевая группа по торговле машинным зрением .

Другими примерами LVDS, используемых в компьютерных шинах, являются HyperTransport и FireWire , оба из которых прослеживают свое развитие до работы после Futurebus , которая также привела к SCI . Кроме того, LVDS - это сигнализация физического уровня в стандартах SCSI (Ultra-2 SCSI и выше), обеспечивающая более высокие скорости передачи данных и большую длину кабелей. Последовательный ATA (SATA), RapidIO и SpaceWire используют LVDS для обеспечения высокоскоростной передачи данных.

Intel и AMD опубликовали пресс-релиз в декабре 2010 года, в котором говорилось, что они больше не будут поддерживать интерфейс ЖК-панели LVDS в своих линейках продуктов к 2013 году. Они продвигают Embedded DisplayPort и Internal DisplayPort в качестве своего предпочтительного решения. Однако интерфейс ЖК-панели LVDS оказался самым дешевым методом перемещения потокового видео с блока обработки видео на контроллер синхронизации ЖК-панели в телевизоре или ноутбуке, и в феврале 2018 года производители ЖК-телевизоров и ноутбуков продолжают внедрять новые продукты с использованием интерфейса LVDS.

LVDS изначально был представлен как стандарт 3,3 В. Масштабируемая сигнализация низкого напряжения ( SLVS ) имеет более низкое синфазное напряжение 200 мВ и уменьшенный размах pp, но в остальном такая же, как LVDS.

Сравнение последовательной и параллельной передачи данных

LVDS работает как в параллельной, так и в последовательной передаче данных . При параллельной передаче несколько дифференциальных пар данных переносят сразу несколько сигналов, включая тактовый сигнал для синхронизации данных. При последовательной связи несколько несимметричных сигналов преобразуются в одну дифференциальную пару со скоростью передачи данных, равной скорости всех объединенных несимметричных каналов. Например, 7-битная параллельная шина, преобразованная в одну пару, будет работать со скоростью, в 7 раз превышающей скорость передачи данных одного несимметричного канала. Устройства для преобразования между последовательными и параллельными данными - это сериализатор и десериализатор, сокращенно SerDes, когда два устройства содержатся в одной интегральной схеме.

Последовательная передача данных также позволяет встроить часы в поток последовательных данных. Это устраняет необходимость в параллельных часах для синхронизации данных. Есть несколько методов для встраивания часов в поток данных. Один из методов - это вставка 2 дополнительных битов в поток данных в качестве стартового и стопового бита, чтобы гарантировать переходы битов через равные промежутки времени для имитации тактового сигнала. Другой метод - кодирование 8b / 10b.

Передача LVDS с кодировкой 8b / 10b

LVDS не определяет схему битового кодирования, потому что это стандарт только физического уровня. LVDS поддерживает любую заданную пользователем схему кодирования для отправки и получения данных по каналу LVDS, включая данные в кодировке 8b / 10b. Схема кодирования 8b / 10b включает информацию о тактовом сигнале и имеет дополнительное преимущество в виде баланса постоянного тока. Баланс постоянного тока необходим для трактов передачи по переменному току (таких как емкостные тракты или тракты с трансформаторной связью). Существуют также методы кодирования с балансировкой постоянного тока для встроенных часов начального / стопового битов, которые обычно включают метод скремблирования данных. Ключевым моментом в LVDS является сигнализация физического уровня для передачи битов по проводам. Он совместим практически со всеми методами кодирования данных и встраивания часов.

LVDS для приложений с очень высокой пропускной способностью данных

Когда одна дифференциальная пара последовательных данных недостаточно высока, существуют методы для параллельного группирования последовательных каналов данных и добавления параллельного тактового канала для синхронизации. Это метод, используемый FPD-Link. Другими примерами параллельного LVDS с использованием нескольких пар LVDS и параллельных часов для синхронизации являются Channel Link и HyperTransport .

Существует также метод увеличения пропускной способности данных путем группирования нескольких каналов данных LVDS со встроенными часами вместе. Однако это не параллельный LVDS, потому что нет параллельных часов, и каждый канал имеет свою собственную информацию о часах. Примером этого метода является PCI Express, где 2, 4 или 8 последовательных каналов с кодировкой 8b / 10b переносят данные приложения от источника к месту назначения. В этом случае место назначения должно использовать метод синхронизации данных для выравнивания нескольких последовательных каналов данных.

Многоточечный LVDS

Двухточечный LVDS обычно работает при 3,5 мА. Многоточечный LVDS или шина LVDS (B-LVDS) могут работать до 12 мА.

Автобусы LVDS и LVDM (от TI ) де-факто являются стандартами многоточечных LVDS. Многоточечный LVDS ( MLVDS ) является TIA стандарт (TIA-899). Стандарт AdvancedTCA определяет MLVDS для распределения часов по объединительной плате на каждую из плат вычислительных модулей в системе.

MLVDS имеет два типа приемников. Тип 1 совместим с LVDS и использует порог +/- 50 мВ. Приемники типа 2 позволяют передавать сигналы проводным способом с устройствами M-LVDS. Для M-LVDS:

SCI-LVDS

Существующей форме LVDS предшествовал более ранний стандарт, инициированный Scalable Coherent Interconnect (SCI). SCI-LVDS был подмножеством семейства стандартов SCI и определен в стандарте IEEE 1596.3 1995 г. Комитет SCI разработал LVDS для соединения многопроцессорных систем с высокоскоростным интерфейсом с низким энергопотреблением, чтобы заменить положительную эмиттерно-связанную логику (PECL).

Стандарты

Стандарт ANSI / TIA / EIA -644-A (опубликован в 2001 г.) определяет LVDS. Первоначально этот стандарт рекомендовал максимальную скорость передачи данных 655 Мбит / с по медной витой паре, но сегодня скорости передачи данных от 1 до 3 Гбит / с распространены в средах передачи высокого качества. Сегодня технологии широкополосной передачи цифрового видеосигнала, такие как LVDS, также используются в транспортных средствах, в которых сигнал, передаваемый в виде дифференциального сигнала, помогает по причинам ЭМС. Однако необходимо использовать высококачественные экранированные кабели витой пары вместе с тщательно продуманными системами разъемов для кабельной разводки. Альтернативой является использование коаксиальных кабелей. Исследования показали, что, несмотря на упрощенную среду передачи, возможно преобладание как излучения, так и помехоустойчивости в высокочастотном диапазоне. В будущем высокоскоростные видеоподключения могут быть меньше, легче и дешевле в реализации.

Технологии последовательной передачи видео широко используются в автомобиле для соединения камер, дисплеев и устройств управления. Несжатые видеоданные имеют некоторые преимущества для определенных приложений. Протоколы последовательной связи теперь позволяют передавать данные со скоростью от 3 до 4 Гбит / с и, таким образом, управлять дисплеями с разрешением до Full HD. Интеграция компонентов сериализатора и десериализатора в блок управления из-за низких требований к дополнительному оборудованию и программному обеспечению - простая и недорогая. Напротив, требуются шинные решения для передачи видео, подключение к соответствующему сетевому контроллеру и, при необходимости, ресурсы для сжатия данных. Поскольку для многих приложений полнофункциональная сеть не требуется во всей видеоархитектуре, а для некоторых соединений сжатие данных невозможно из-за потери качества изображения и дополнительной задержки, технологии передачи видео с ориентацией на шину в настоящее время привлекательны лишь частично.

Читайте также: